Ningbo Sibranch Microelectronics Teknoloji co, Ltd.:Fabricant ou fè konfyans Silisyòm Wafer Substrate!

Te fonde an 2006 pa syans materyèl ak jeni syantis nan Ningbo, Lachin, Sibranch Microelectronics gen pou objaktif pou bay semiconductor wafer ak sèvis nan tout mond lan. Pwensipal pwodwi nou yo ki gen ladan estanda Silisyòm gauf SSP (sèl bò poli), DSP (Double bò poli), tès Silisyòm gauf ak premye Silisyòm wafers, SOI (Silisyòm sou Izolan) wafer ak coinroll wafers ak dyamèt jiska 12 pous, CZ/MCZ/ FZ/NTD, prèske nenpòt oryantasyon, koupe koupe, segondè ak ba rezistivite, ultra plat, ultra mens, epè gauf elatriye.

Dirijan Sèvis

Nou angaje nan toujou ap inovasyon pwodwi nou yo bay kliyan etranje ak yon gwo kantite bon jan kalite pwodwi depase satisfaksyon kliyan. Nou kapab tou bay sèvis Customized selon kondisyon kliyan yo tankou gwosè, koulè, aparans, elatriye Nou ka bay pri ki pi favorab ak bon jan kalite pwodwi.

Kalite garanti

Nou te kontinyèlman rechèch ak inovasyon satisfè bezwen yo nan kliyan diferan. An menm tan an, nou toujou respekte kontwòl kalite strik pou asire ke bon jan kalite a nan chak pwodwi satisfè estanda entènasyonal yo.

Wide Komèsyal Peyi

Nou konsantre sou lavant nan mache lòt bò dlo. Pwodwi nou yo ekspòte nan Ewòp, Amerik, Azi Sidès, Mwayen Oryan ak lòt rejyon yo, epi yo byen resevwa pa kliyan atravè mond lan.

Divès kalite pwodwi

Konpayi nou an ofri sèvis pwosesis Customized Silisyòm ki adapte pou satisfè bezwen espesifik kliyan nou yo. Men sa yo enkli Si Wafer BackGrinding, Dicing, DownSizing, Edge Grinding, osi byen ke MEMS nan mitan lòt moun. Nou fè efò pou nou bay solisyon ki ta dwe depase atant epi asire satisfaksyon kliyan yo.

CZ Silisyòm Wafer yo koupe soti nan lengote Silisyòm kristal sèl rale lè l sèvi avèk Czochralski CZ kwasans metòd, ki pi lajman itilize nan endistri elektwonik la grandi kristal Silisyòm soti nan gwo lengote Silisyòm silendrik yo itilize pou fabrike aparèy semi-conducteurs. Nan pwosesis sa a, yon grenn Silisyòm cristalline long ak tolerans oryantasyon egzak prezante nan yon pisin Silisyòm fonn ak tanperati jisteman kontwole. Se kristal grenn nan tou dousman rale anwo soti nan fonn nan yon pousantaj estrikteman kontwole, ak solidifikasyon kristal nan atòm yo faz likid rive nan koòdone la. Pandan pwosesis sa a rale, kristal grenn nan ak kreze a wotasyon nan direksyon opoze, fòme yon gwo Silisyòm kristal sèl ak yon estrikti kristal pafè nan pitit pitit la.

Silisyòm oksid wafer se yon materyèl avanse ak esansyèl yo itilize nan divès kalite endistri gwo teknoloji ak aplikasyon. Li se yon sibstans ki wo-pite cristalline ki te pwodwi pa trete bon jan kalite materyèl Silisyòm, fè li yon substra ideyal pou anpil diferan kalite aplikasyon elektwonik ak fotonik.

Enbesil wafers (yo rele tou kòm wafers tès) se wafers pwensipalman te itilize pou eksperyans ak tès Et être diferan de jeneral wafers pou pwodwi. An konsekans, wafers reklame yo sitou aplike kòm wafers enbesil (gafrettes tès).

Silisyòm wafers ki kouvri ak lò, ak chips Silisyòm kouvwi lò yo itilize anpil kòm substrats pou karakterizasyon analyse materyèl yo. Pou egzanp, materyèl ki depoze sou plak lò ki kouvri yo ka analize atravè elipsometri, espektroskopi Raman oswa espektroskopi enfrawouj (IR) akòz gwo-reflektif ak pwopriyete optik favorab nan lò.

Silisyòm Epitaxial Wafers yo trè versatile epi yo ka fabrike nan yon seri de gwosè ak epesè adapte kondisyon endistri diferan. Yo itilize yo tou nan yon varyete aplikasyon, ki gen ladan sikui entegre, mikropwosè, detèktè, elektwonik pouvwa, ak fotovoltaik.

Manifaktire lè l sèvi avèk dènye teknoloji a epi li fèt pou ofri fyab san parèy ak konsistans nan pèfòmans. Tèmik oksid sèk ak mouye se yon zouti esansyèl pou manifaktirè semi-conducteurs atravè lemond paske li bay yon fason efikas pou pwodwi bon jan kalite wafers ki satisfè tout egzijans endistri a.

Wafer sa a gen yon dyamèt 300 milimèt, ki fè li pi gwo pase gwosè wafer tradisyonèl yo. Gwosè sa a pi gwo fè li pi pri-efikas ak efikas, sa ki pèmèt pou pi gwo pwodiksyon pwodiksyon san sakrifye bon jan kalite.

Wafer Silisyòm 200mm la tou versatile nan aplikasyon li yo, ak aplikasyon nan rechèch ak devlopman, osi byen ke nan manifakti gwo volim. Li ka Customized nan espesifikasyon egzak ou a, ak opsyon pou gauf mens oswa epè, sifas poli oswa unpolished, ak lòt karakteristik ki baze sou bezwen espesifik ou yo.

Silisyòm wafer 100mm se yon bon jan kalite pwodwi ki lajman itilize nan endistri elektwonik ak semi-conducteurs. Wafer sa a fèt pou bay pi bon pèfòmans, presizyon, ak fyab ki esansyèl nan fabrikasyon aparèy semi-conducteurs.

Ki sa ki Silisyòm Wafer Substrate

Silisyòm wafer substrats se yon pati enpòtan nan manifakti semi-conducteurs entegre sikui ak aparèy. Nan nwayo yo, yo tou senpleman bay yon fondasyon solid - literalman yon substra - sou ki sikui mikwoelektwonik yo ka konstwi atravè fotolitografi konplike ak etap fabwikasyon. Sepandan, substrats Silisyòm enpak pi plis pase jis bay ICs yon sifas ki plat pou konstwi sou. Pwopriyete cristalline ak elektwonik nan wafer nan substra tèt li yo enpòtan anpil nan detèmine kapasite yo pèfòmans ultim nan aparèy ki fèt sou tèt. Faktè tankou oryantasyon kristal, pite chimik, dansite defo lasi, ak karakteristik rezistans elektrik yo dwe byen kontwole ak optimize pandan fabrikasyon substrate.

Pwopriyete Silisyòm Wafer Substrate

Rezistivite

Kòm mansyone anvan, rezistivite endike konbyen wafer la anpeche koule elèktron. Pifò aparèy mande pou substrats ak ranje rezistans presi. Sa a se reyalize pa dopaj Silisyòm nan ak enpurte - pi souvan bor (pou p-tip) oswa fosfò (pou n-tip).

Tipik Silisyòm Wafer Rezistivite Substrate:

1-30 Ω-cm - rezistans ki ba, yo itilize pou lojik CMOS

30-100 Ω-cm - substrats epitaxial

1000 Ω-cm - rezistans segondè, yo itilize pou aparèy RF

Flatness / Lis

Flatness sifas mezire ki jan planar sifas substra a se, pandan y ap lis endike brutality. Tou de enpòtan pou modèl fotolitografi pwòp epi asire aparèy yo bati kòrèkteman. Flatness yo quantifye lè l sèvi avèk yon mezi ki rele Varyasyon epesè total (TTV). Bon plat yo gen TTV < 10 μm atravè wafer la. Lis oswa brutality mezire lè l sèvi avèk Rasin Mean Squared (RMS). Substra fen segondè yo gen RMS brutality <0.5 nm.

Faktori Silisyòm Wafer Substrate

Pwodui bon jan kalite substrats wafer Silisyòm se yon gwo defi teknik ki mande teknik manifakti avanse. Isit la se yon apèsi rapid:

Kwasans ingot

Tout bagay kòmanse ak grandi lengote yon sèl kristal lè l sèvi avèk metòd Czochralski. Nan pwosesis sa a, moso nan polysilicon ultrapure yo chaje nan yon kreze kwatz epi yo fonn. Yon ti sèl kristal "grenn" bese jiskaske li jis manyen sifas la fonn, Lè sa a, tou dousman retire anwo. Kòm kristal grenn nan rale moute, silikon likid solidifye sou li, ki pèmèt yon gwo kristal sèl yo dwe grandi.

Atòm enpurte yo ak anpil atansyon ajoute pou dope ingot la nan rezistivite espesifye. Dopan komen yo se bor ak fosfò. Se refwadisman jisteman kontwole asire defo san kwasans kristal.

Tranch

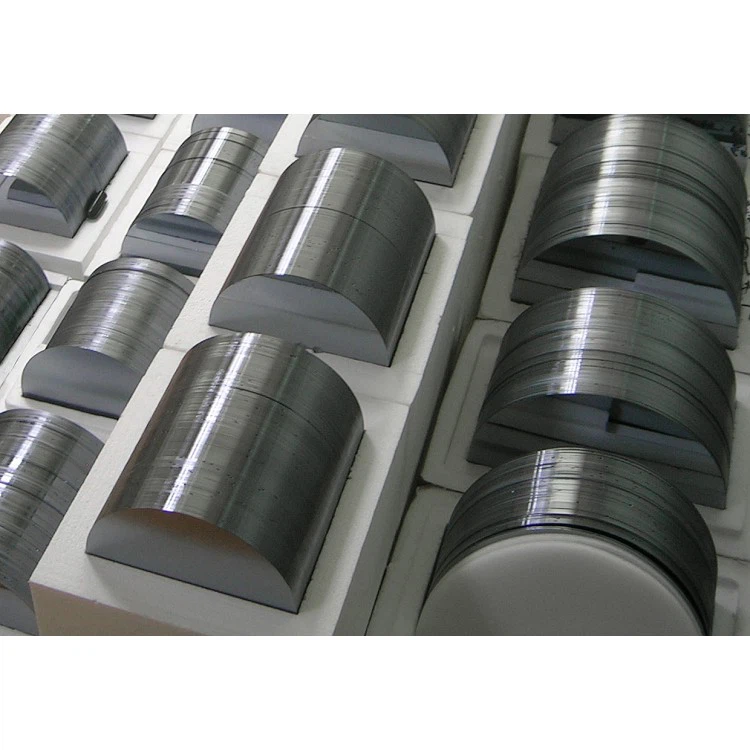

Se gwo ingot kristal sèl la tranche nan wafers endividyèl lè l sèvi avèk sci dyamèt entèn yo. Diamond embedded lam kontinyèlman koupe tranch trè mens soti nan tout ingot la ansanm. Yo itilize likid refwadisman pou minimize domaj nan friksyon ak chofaj.

Tranche dwe trè presi pou asire epesè wafer inifòm ak plat. Epesè sib se alantou 0.7 mm.

Lape

Apre tranche, gaufre yo gen sifas ki graj modera. Yo itilize yon pwosesis abrazif pou plati yo. Sa a enplike nan fòse chak sifas wafer kont yon plak lap fè jete ki kouvri ak yon sispansyon abrazif. Plak la wotasyon pandan y ap jisteman kontwole presyon yo aplike soti nan sifas la wafer.

Lapping retire materyèl respire nan sifas la pandan y ap plati nenpòt ki protrusions oswa krèt kite nan tranche. Sa a ede amelyore platite an jeneral wafer.

Gravure

Lapping ka pwovoke kèk domaj sifas jiska 10-15 μm pwofondè. Sa a se retire nan grave sifas la lè l sèvi avèk melanj de pwodui chimik asid oswa alkalin. Gravure fonn Silisyòm nan yon vitès kontwole pou retire domaj lapping, kite yon sifas pwòp san domaj pou polisaj final la.

Polisaj

Dènye etap la se pwodwi yon sifas ki pa lis, san domaj lè l sèvi avèk yon pwosesis polisaj. Sa a sèvi ak mekanik menm jan ak lapping men ak alkalin koloidal silik polisaj olye pou yo abrazif. Etap polisaj la elimine domaj anba sifas nan etap anvan yo.

Polisaj ap kontinye jiskaske yo rive nan spesifikasyon rugosite RMS sifas vle. Anpil sik polisaj presizyon ka bezwen pou reyalize yon sèl chif angstrom brutality.

Kisa pou w konnen lè w ap itilize Silisyòm Wafer Substrate

Twòp estrès ak presyon ki soti nan grafing, lyezon fil, separe mouri, ak operasyon anbalaj ka lakòz yon wafer Silisyòm vin frajil oswa krak. Sa a kalite echèk oswa domaj ka afekte durability nan wafer la epi li ka rann li initil.

Ekspansyon tèmik refere a tandans nan matyè a elaji oswa chanje volim li, fòm, oswa zòn akòz chanjman tanperati. Se konsa, lè yon substra sibi chalè pi lwen pase sa li kapab pote, li ka lakòz fann oswa kraze.

Defo kristalografi ki egziste deja, tankou dislokasyon, presipite oksijèn, ak fay anpile, nan tou de wafer nan Silisyòm ak kouch epitaxial, ka konpwomèt bon jan kalite a nan wafer la ak mennen nan domaj. Defo sa yo ka lakòz siyifikatif, kouran flit nòmal koule oswa kreye tiyo ki ba-rezistans, ki ka kout sikwi junctions.

Efè difizyon ak enplantasyon ion tankou diferan fenomèn difizyon anòmal ki lye ak konbinezon espesifik kristal oswa domaj dopant ak reyaksyon presipite metal kontaminan ka afekte kalite wafer la epi echwe.

Bagay ou dwe konsidere lè w ap manyen ak estoke Silisyòm Wafer substrats

Kontwole Anviwònman Cleanroom: Kenbe Kondisyon Optimal yo

Nan fabwikasyon semi-conducteurs, anviwònman sal pwòp yo metikuleusement kontwole pou misyon pou minimize risk kontaminasyon ak garanti bon jan kalite ki pi wo nan substrats wafer Silisyòm. Anviwònman sa yo anjeneral konfòme yo ak estanda pwòpte strik, tankou ISO Klas 1 oswa Klas 10 chanm pwòp, kote kantite patikil ki nan lè yo byen kontwole pou chak mèt kib lè. Cleanrooms gen sistèm filtraj espesyalize ki kontinyèlman retire patikil nan lè a pou kenbe kondisyon optimal yo. Filtè segondè-efikasite patikil lè (HEPA) ak filtè ultra-ba patikil lè (ULPA) pran patikil ki piti tankou 0.3 mikron ak 0.12 mikron, respektivman.

Diminye Risk Dechaj Elektwostatik: Pwoteje Kont Domaj

Egzeyat elektwostatik poze yon menas enpòtan pou substrats wafer Silisyòm pandan manyen ak depo. Enstalasyon semi-conducteurs aplike mezi kontwòl estatik tankou espageti baz, souflè lè iyonize, ak planche kondiktif pou gaye chaj estatik ak anpeche domaj nan gauf. Pèsonèl mete espageti tè pou dechaje elektrisite estatik san danje nan kò yo pandan y ap ionize souflè lè netralize chaj estatik sou sifas yo. Materyèl planche kondiktif pèmèt chaj estatik gaye san danje nan tè a, diminye risk pou evènman egzeyat elektwostatik.

Solisyon Anbalaj Pwotektif: Pwoteksyon Kont Mal

Anbalaj apwopriye enpòtan anpil pou pwoteje substrats wafer Silisyòm kont domaj fizik, kontaminasyon, ak imidite pandan transpò ak depo. Enstalasyon semi-kondiktè yo sèvi ak divès kalite solisyon anbalaj pwoteksyon pou pwoteje wafers epi kenbe entegrite yo nan tout chèn ekipman pou. Yon solisyon anbalaj komen se anbalaj vakyòm-sele, kote wafers Silisyòm yo mete nan yon sak sele oswa veso ak vakyòm-sele pou retire lè epi kreye yon baryè pwoteksyon kont kontaminan ak imidite. Pake desiccant yo souvan enkli nan anbalaj la pou absòbe imidite rezidyèl epi kenbe yon anviwònman sèk.

Aderans a Pwotokòl Manyen: Precision ak Swen

Aderans strik nan pwotokòl manyen se esansyèl pou minimize risk pandan fabrikasyon wafer ak asanble. Enstalasyon semi-conducteurs devlope pwosedi manyen detaye ak pwotokòl ki dekri pi bon pratik pou transpòte, manipile ak trete wafers Silisyòm san danje. Pwotokòl manyen sa yo anjeneral kouvri yon pakèt aktivite, tankou chaje ak dechaje wafer, enspeksyon wafer, pwosesis chimik, ak manipilasyon mekanik. Yo bay enstriksyon etap pa etap pou chak travay, espesifye ekipman yo dwe itilize, teknik apwopriye yo dwe swiv, ak prekosyon sekirite yo dwe obsève.

Sistèm Suivi ak Trase: Asire Responsablite ak Trasabilite

Sistèm idantifikasyon ak swiv solid bay responsablite ak trasabilite nan tout pwosesis fabrikasyon semi-conducteurs la. Sistèm sa yo bay yon idantifyan inik nan chak substrate wafer Silisyòm, ki gen enfòmasyon sou orijin li, istwa pwosesis, ak rezilta enspeksyon kalite. Yon metòd idantifikasyon wafer komen se lè l sèvi avèk kòd bar oswa tags idantifikasyon radyo-frekans (RFID), aplike nan wafers nan plizyè etap nan fabrikasyon. Idantifyan sa yo analize ak anrejistre nan chak etap nan pwosesis pwodiksyon an, sa ki pèmèt enstalasyon semi-conducteurs yo swiv mouvman an ak estati wafers an tan reyèl.

Kondisyon Depo Optimal: Prezève Kalite sou tan

Kondisyon depo apwopriye yo kritik pou kenbe bon jan kalite a ak entegrite nan substrats wafer Silisyòm nan tout pwosesis la fabrikasyon semi-conducteurs. Enstalasyon semi-kondiktè yo kenbe zòn depo dedye nan anviwònman sal pwòp, ekipe ak kabinèt ak etajè klimatik kontwole pou prezève wafers nan kondisyon optimal. Tanperati ak imidite kontwòl esansyèl pou anpeche degradasyon ak asire estabilite nan wafers Silisyòm pandan depo. Enstalasyon semi-conducteurs anjeneral kenbe tanperati depo ant 18 degre ak 22 degre ak nivo imidite ant 40% ak 60% pou minimize risk pou domaj ki gen rapò ak imidite ak kontaminasyon.

FAQ

Poukisa Chwazi Nou

Pwodwi nou yo soti sèlman nan senk pi gwo manifaktirè nan mond lan ak dirijan faktori domestik. Sipòte pa ekip teknik domestik ak entènasyonal trè kalifye ak mezi kontwòl kalite sevè.

Objektif nou se bay kliyan sipò konplè youn-a-yon sèl, asire lis chanèl kominikasyon ki pwofesyonèl, alè, ak efikas. Nou ofri yon kantite minimòm lòd ki ba ak garanti livrezon rapid nan 24 èdtan.

Montre faktori

Envantè vas nou an konsiste de 1000+ pwodwi, asire ke kliyan yo ka pase lòd pou yon ti kras tankou yon sèl pyès. Ekipman pwòp tèt ou nou yo pou dicing & backgrinding, ak koperasyon konplè nan chèn endistriyèl mondyal la pèmèt nou rapid chajman asire kliyan satisfaksyon yon sèl-stop ak konvenyans.

Sètifika nou an

Konpayi nou an fyè de sètifikasyon divès kalite nou te touche, ki gen ladan sètifika patant nou an, sètifika ISO9001, ak sètifika National High-Tech Enterprise. Sètifikasyon sa yo reprezante devouman nou pou inovasyon, jesyon kalite, ak angajman pou ekselans.

Baj popilè: Silisyòm wafer substrate, Lachin Silisyòm wafer substrate manifaktirè, Swèd, faktori