Silisyòm wafers yo se poto materyèl semi-conducteurs. Yo premye fè nan baton Silisyòm pa rale kristal sèl, ak Lè sa a, koupe ak fè. Depi kantite elektwon valans nan atòm Silisyòm se 4 ak nimewo ordinal la modere, Silisyòm gen pwopriyete espesyal fizik ak chimik epi yo ka itilize nan pwodui chimik, fotovoltaik, chip ak lòt jaden. Espesyalman nan jaden an nan chips, li se pwopriyete yo semi-conducteurs nan Silisyòm ki fè li poto a nan chips. Nan jaden an nan fotovoltaik, li ka itilize pou jenerasyon pouvwa solè. Anplis, Silisyòm konte pou 25.8% nan kwout tè a. Li relativman pratik pou m 'epi li gen resiklaj fò, kidonk pri a ba, ki plis amelyore seri aplikasyon Silisyòm.

1. Silisyòm - poto a nan materyèl chip materyèl Silisyòm yo divize an Silisyòm kristal sèl ak Silisyòm polikristalin dapre aranjman nan diferan nan selil inite. Pi gwo diferans ki genyen ant Silisyòm kristal sèl ak Silisyòm polikristalin se ke aranjman selil inite nan Silisyòm kristal sèl se lòd, pandan y ap Silisyòm polikristalin dezòdone. An tèm de metòd fabrikasyon, Silisyòm polikristalin jeneralman fèt pa dirèkteman vide materyèl Silisyòm nan yon kreze pou fonn li ak Lè sa a, refwadi li. Silisyòm monokristalin fòme nan yon baton kristal pa rale yon kristal sèl (metòd Czochralski). An tèm de pwopriyete fizik, karakteristik sa yo nan de kalite Silisyòm yo byen diferan. Silisyòm monokristalin gen konduktiviti elektrik fò ak efikasite konvèsyon fotoelektrik segondè. Efikasite konvèsyon foto-elektrik nan Silisyòm monokristalin se jeneralman alantou 17% a 25%, pandan y ap efikasite nan Silisyòm polikristalin se pi ba pase 15%.

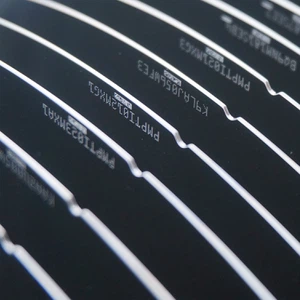

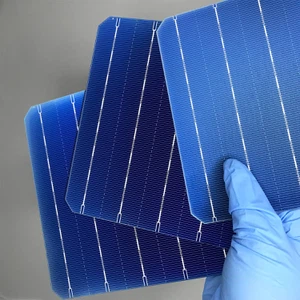

▲ Semiconductor Silisyòm wafers ak fotovoltaik Silisyòm wafers

▲Single kristal Silisyòm inite selil estrikti

Silisyòm fotovoltaik:Akòz efè a foto-elektrik ak avantaj evidan nan Silisyòm monokristalin, moun sèvi ak Silisyòm wafers ranpli konvèsyon nan enèji solè nan enèji elektrik. Nan jaden an fotovoltaik, yo jeneralman itilize selil kare monokristalin Silisyòm ak kwen awondi. Pi bon mache silisyòm polikristalin yo itilize tou, men efikasite konvèsyon an pi ba.

▲ Devan ak dèyè selil monokristalin Silisyòm

▲ Selil Silisyòm polikristalin devan ak dèyè

Depi fotovoltaik Silisyòm wafers gen kondisyon ki ba pou paramèt tankou pite ak deformation, pwosesis fabrikasyon an se relativman senp. Lè w pran selil monokristalin Silisyòm kòm egzanp, premye etap la se koupe ak wonn. Premyèman, koupe baton Silisyòm monokristalin nan baton kare selon kondisyon gwosè yo, ak Lè sa a, wonn kat kwen yo nan branch bwa kare yo. Dezyèm etap la se marinated, ki se sitou yo retire enpurte sifas nan branch bwa kare monokristalin yo. Twazyèm etap la se tranche. Premyèman, kole branch bwa kare netwaye yo sou tablo travay la. Lè sa a, mete tablo travay la sou slicer la epi koupe li selon paramèt pwosesis yo mete. Finalman, netwaye silisyòm monokristalin yo epi kontwole lis sifas, rezistivite ak lòt paramèt.

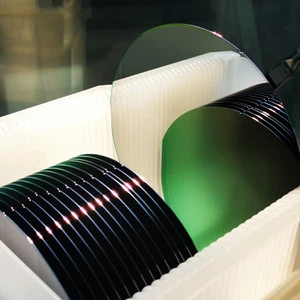

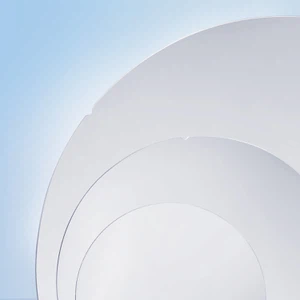

Semiconductor Silisyòm wafers:Semiconductor Silisyòm wafers gen pi wo kondisyon pase fotovoltaïque Silisyòm wafers. Premyèman, tout wafers Silisyòm yo itilize nan endistri semi-conducteurs yo se Silisyòm monokristalin, yo nan lòd yo asire menm pwopriyete elektrik nan chak pozisyon nan wafer Silisyòm lan. An tèm de fòm ak gwosè, fotovoltaik monokristalin Silisyòm wafers yo kare, sitou ak longè bò 125mm, 150mm, ak 156mm. Silisyòm monokristalin yo itilize pou semi-conducteurs yo wonn, ak dyamèt 150mm (6-pous wafers), 200mm (8-pous wafers) ak 300mm (12-pous wafers). An tèm de pite, egzijans pou pite pou silisyòm monokristalin yo itilize pou fotovoltaik se ant 4N-6N (99.99%-99.9999%), men egzijans pou pite pou silisyòm monokristalin yo itilize pou semi-conducteurs se alantou. 9N (99.9999999%) -11N (99.999999999%), ak kondisyon pou pite minimòm lan se 1000 fwa sa yo ki nan silisyòm wafers monokristalin yo itilize pou fotovoltaik. An tèm de aparans, platite sifas, lis ak pwòpte nan gauf Silisyòm yo itilize pou semi-conducteurs yo pi wo pase sa yo ki nan gauf Silisyòm yo itilize pou fotovoltaik. Pite se pi gwo diferans ki genyen ant silisyòm monokristalin yo itilize pou fotovoltaik ak silisyòm monokristalin yo itilize pou semi-conducteurs.

▲ Semiconductor Silisyòm wafer pwosesis manifakti

Devlopman Lwa Moore se devlopman silisyòm wafers. Depi semi-conducteurs Silisyòm wafers yo wonn, semi-conducteurs Silisyòm wafers yo rele tou "Silisyòm gaufrettes" ou "wafers". Wafers yo se "substra" pou fabrikasyon chip, ak tout chips yo fabrike sou "substra" sa a. Nan istwa devlopman semi-conducteurs Silisyòm, gen de direksyon prensipal: gwosè ak estrikti.

An tèm de gwosè, chemen devlopman nan silisyòm wafers ap vin pi gwo ak pi gwo: nan etap nan byen bonè nan devlopman sikwi entegre, 0.75-pous wafers yo te itilize. Ogmante zòn nan wafer ak kantite chips sou yon sèl wafer ka diminye depans yo. Anviwon 1965, ak entwodiksyon de Lwa Moore, tou de teknoloji sikwi entegre ak silisyòm wafers inogire nan yon peryòd de devlopman rapid. Silisyòm wafers te pase nan 4-pous, 6-pous, 8-pous ak 12-pous nœuds. Depi Intel ak IBM te devlope ansanm fabrikasyon chip wafer 12-pous an 2001, wafer Silisyòm endikap aktyèl la se 12-pous wafers, kontablite pou apeprè 70%, men 18-pous (450mm) wafers gen yo te mete sou ajanda a.

▲ Paramèt diferan gwosè wafer

▲ Devlopman gwosè wafer Silisyòm

An tèm de estrikti, direksyon devlopman nan silisyòm wafers ap vin pi plis ak plis konplèks: nan etap nan byen bonè nan devlopman sikwi entegre, te gen yon sèl kalite chip lojik, men ak nimewo a ogmante nan senaryo aplikasyon, chips lojik, aparèy pouvwa. , chips analòg, chips melanje analòg ak dijital, chips depo flash / DRAM, chips frekans radyo, elatriye te parèt youn apre lòt, fè silisyòm wafers gen diferan fòm estriktirèl. Koulye a, gen sitou twa kalite:

PW (Wafer Polonè):wafer poli. Silisyòm wafers yo dirèkteman koupe apre rale yon sèl kristal yo pa pafè nan lis oswa deformation, kidonk yo dwe premye poli. Metòd sa a se tou fason ki pi primitif pou trete gaufre Silisyòm.

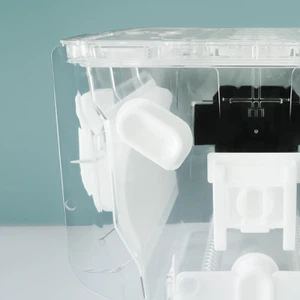

AW (Anneal Wafer):Wafer rkwit. Avèk devlopman kontinyèl nan teknoloji pwosesis ak rediksyon kontinyèl nan gwosè karakteristik tranzistò, enpèfeksyon yo nan gauf poli yo piti piti ekspoze, tankou domaj lokal lasi sou sifas la nan Silisyòm gauf ak kontni oksijèn segondè sou sifas la nan Silisyòm gauf. Yo nan lòd yo rezoud pwoblèm sa yo, yo te devlope teknoloji annealing wafer. Apre polisaj, yo mete wafer Silisyòm lan nan yon tib founo plen ak gaz inaktif (anjeneral agon) pou rkwir tanperati ki wo. Sa a ka pa sèlman repare domaj yo lasi sou sifas la nan wafer a Silisyòm, men tou, diminye kontni an oksijèn sifas yo.

EW (gaf epitaksi):wafer epitaxial Silisyòm. Avèk senaryo aplikasyon yo ogmante nan sikui entegre, estanda Silisyòm wafers manifaktire pa faktori wafer Silisyòm pa ka satisfè kondisyon yo nan kèk pwodwi an tèm de pwopriyete elektrik. An menm tan an, domaj yo lasi redwi pa annealing tèmik pa ka satisfè kondisyon yo de pli zan pli pi piti lajè liy. Sa a te mennen nan Aparisyon nan wafers Silisyòm epitaxial. Kouch epitaxial abityèl la se yon fim mens Silisyòm. Yon kouch fim mens Silisyòm grandi sou baz wafer Silisyòm orijinal la lè l sèvi avèk teknoloji depo fim mens. Depi substrate Silisyòm egziste kòm yon kristal grenn nan epitaksi Silisyòm, kwasans lan nan kouch epitaxial la pral repwodui estrikti kristal la nan wafer Silisyòm lan. Depi wafer Silisyòm substrate a se yon sèl kristal, kouch epitaxial la se tou yon sèl kristal. Sepandan, depi li pa poli, domaj yo lasi sou sifas wafer Silisyòm apre kwasans yo ka redwi a yon nivo ki ba anpil.

Endikatè epitaksi teknik sitou gen ladan epesè kouch epitaksi ak inifòmite li yo, inifòmite rezistivite, kontwòl metal kò, kontwòl patikil, defo anpile, dislokasyon ak lòt kontwòl domaj. Nan etap sa a, moun yo te reyalize bon jan kalite segondè epitaksi Silisyòm wafer pa optimize tanperati reyaksyon epitaksi, to koule gaz epitaksi, ak sant ak kwen tanperati gradyan. Akòz pwodwi diferan ak bezwen pou amelyorasyon teknolojik, pwosesis epitaxial la te kontinyèlman optimize pou reyalize bon jan kalite segondè epitaxial wafer Silisyòm.

Anplis de sa, teknoloji aktyèl la ka jenere kouch epitaxial ak eleman dopan rezistans ak konsantrasyon dopan diferan de sa yo ki nan wafer Silisyòm orijinal la, ki fè li pi fasil kontwole pwopriyete elektrik yo nan wafer Silisyòm grandi. Pou egzanp, yon kouch N-tip Silisyòm epitaxial kouch ka pwodwi sou yon wafer Silisyòm P-kalite, konsa fòme yon ba-konsantrasyon doped PN junction, ki ka optimize vòltaj la pann ak redwi efè a latch nan manifakti chip ki vin apre. Epesè kouch epitaxial la jeneralman varye selon senaryo itilizasyon an. Anjeneral, epesè chip lojik la se apeprè 0.5 mikron a 5 mikron, ak epesè aparèy pouvwa a se apeprè 50 mikron a 100 mikron paske li bezwen kenbe tèt ak vòltaj segondè.

▲ Pwosesis kwasans wafer epitaxial Silisyòm

▲ Diferan dopaj nan wafers epitaxial

SW (SOI Wafer):SOI la vle di Silicon-On-Insulator. Silisyòm SOI yo souvan itilize nan chips devan RF paske nan avantaj yo tankou ti kapasite parazit, ti efè chanèl kout, gwo dansite eritaj, gwo vitès, konsomasyon pouvwa ki ba, ak bri substrate espesyalman ba.

▲ Òdinè estrikti Silisyòm MOS

▲SOI Silisyòm wafer MOS estrikti

Gen kat metòd prensipal pou fabrike silisyòm SOI:Teknoloji SIMOX, teknoloji lyezon, teknoloji Sim-bond ak teknoloji Smart-CutTM; prensip la nan SOI Silisyòm wafers se relativman senp, ak objektif debaz la se ajoute yon kouch posibilite (jeneralman sitou Silisyòm diyoksid SiO2) nan mitan an nan substra a.

▲ Kat teknoloji pou fabrike SOI wafers

Soti nan pèspektiv nan paramèt pèfòmans, Smart-CutTM teknoloji se pèfòmans ki pi ekselan nan aktyèl SOI Silisyòm Wafer teknoloji fabrikasyon an. Pèfòmans teknoloji Simbond la pa anpil diferan de teknoloji Smart-Cut, men an tèm de epesè Silisyòm tèt la, wafer Silisyòm SOI ki te pwodwi pa teknoloji Smart-Cut se pi mens, epi nan pèspektiv pri pwodiksyon, Smart. -Teknoloji koupe ka réutiliser gaufres Silisyòm. Pou pwodiksyon an mas nan lavni, teknoloji Smart-Cut gen plis avantaj pri, kidonk endistri a kounye a jeneralman rekonèt teknoloji Smart-Cut kòm direksyon devlopman nan lavni nan gauf Silisyòm SOI.

▲ Konparezon pèfòmans diferan teknoloji manifakti wafer SOI

SIMOX teknoloji: SIMOX la vle di Separasyon pa oksijèn implanté. Atòm oksijèn yo enjekte nan wafer la, ak Lè sa a, rkwit nan tanperati ki wo pou reyaji ak atòm Silisyòm ki antoure yo pou fòme yon kouch diyoksid Silisyòm. Difikilte pou teknoloji sa a se kontwole pwofondè ak epesè enplantasyon ion oksijèn. Li gen gwo kondisyon pou teknoloji implantation ion.

Teknoloji Liaison: Liaison teknoloji yo rele tou Liaison teknoloji. Silisyòm wafers SOI fèt pa Liaison yo rele tou Bonded SOI, oswa BSOI pou kout. Teknoloji Liaison mande de gaufret Silisyòm òdinè, youn nan yo grandi ak yon kouch oksid (SiO2), ak Lè sa a, estokaj ak yon lòt sous Silisyòm. Koneksyon an se kouch oksid la. Finalman, li se tè ak poli nan pwofondè a vle nan kouch la antere l '(SiO2). Piske teknoloji lyezon pi senp pase teknoloji implantation ion, pifò silisyòm SOI yo kounye a fèt ak teknoloji lyezon.

▲ Silisyòm-sou-izolan

▲ Metòd lyezon wafer pou fòme Silisyòm sou izolan

Teknoloji Sim-bond:teknoloji lyezon piki oksijèn. Teknoloji Sim-bond se yon konbinezon de SIMOX ak teknoloji kosyon. Avantaj la se ke epesè nan kouch oksid antere l 'ka kontwole ak presizyon segondè. Premye etap la se enjekte iyon oksijèn nan yon wafer Silisyòm, Lè sa a, rkwit nan tanperati ki wo pou fòme yon kouch oksid, ak Lè sa a, fòme yon kouch oksid SiO2 sou sifas la nan wafer Silisyòm lan. Dezyèm etap la se kosyon wafer Silisyòm nan yon lòt wafer. Lè sa a, recuit nan tanperati ki wo pou fòme yon koòdone lyezon pafè. Twazyèm etap la se pwosesis eklèsi. Eklèsi yo fèt lè l sèvi avèk teknoloji CMP, men kontrèman ak teknoloji kosyon, sim-kosyon gen yon kouch oto-sispann, ki pral otomatikman sispann lè fanm k'ap pile nan kouch SiO2 la. Lè sa a, kouch SiO2 la retire pa grave. Dènye etap la se polisaj.

Smart-cut teknoloji:teknoloji peeling entelijan. Teknoloji Smart-cut se yon ekstansyon nan teknoloji lyezon. Premye etap la se oksidasyon yon wafer ak jenere yon epesè fiks nan SiO2 sou sifas la nan wafer la. Dezyèm etap la se sèvi ak teknoloji implantation ion pou enjekte iyon idwojèn nan yon pwofondè fiks nan wafer la. Twazyèm etap la se kosyon yon lòt wafer nan wafer oksidize a. Katriyèm etap la se sèvi ak ba-tanperati tèmik recuit teknoloji pou fòme bul ak iyon idwojèn, ki lakòz yon pòsyon nan wafer Silisyòm nan dekale. Lè sa a, wo-tanperati tèmik recuit teknoloji ki itilize pou ogmante fòs Liaison. Senkyèm etap la se plati sifas Silisyòm lan. Teknoloji sa a rekonèt entènasyonalman kòm direksyon devlopman SOI teknoloji. Se epesè nan kouch oksid antere l 'konplètman detèmine pa pwofondè nan enplantasyon ion idwojèn, ki se pi egzak. Anplis, wafer la kale ka itilize ankò, ki redwi anpil pri a.

▲ SIM-kosyon metòd pou fòme Silisyòm-sou-izolan

▲ Smart-cut metòd pou fòme Silisyòm-sou-izolan

2. High-baryè manifakti teknoloji 1. Faktori teknoloji

Materyèl anvan tout koreksyon nan gaufre Silisyòm se kwatz, ki se souvan ke yo rekonèt kòm sab, ki ka mine dirèkteman nan lanati. Pwosesis fabrikasyon wafer la ka ranpli nan plizyè etap: sitou dezoksidasyon ak pirifikasyon, raffinage polysilicon, sèl kristal Silisyòm lengote (baton Silisyòm), woule, koupe wafer, polisaj wafer, recuit, tès, anbalaj ak lòt etap.

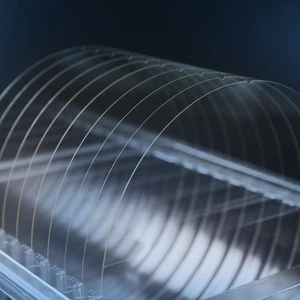

▲ CZ (Czochralski) semiconductor wafer pwosesis manifakti

▲ CZ Farad yon sèl kristal schematic

Deoksidasyon ak pirifikasyon:Premye etap la nan manifakti wafer Silisyòm se deoksidize ak pirifye minrè kwatz la. Pwosesis prensipal yo gen ladan klasman, separasyon mayetik, flotasyon, degaze segondè-tanperati, elatriye enpurte prensipal yo fè ak aliminyòm nan minrè a yo retire.

Rafine polysilicon:Apre yo fin jwenn SiO2 relativman pi, se yon sèl Silisyòm kristal ki pwodui nan reyaksyon chimik. Reyaksyon prensipal la se SiO2+C→Si+CO. Apre reyaksyon an fini, CO evapore dirèkteman, kidonk yo rete sèlman kristal Silisyòm. Nan moman sa a, Silisyòm nan se Silisyòm polikristalin, epi li se Silisyòm brit, ki gen yon anpil nan enpurte. Yo nan lòd yo filtre deyò enpurte depase, silikon brit yo jwenn yo dwe marinated. Asid souvan itilize yo se asid idroklorik (HCl), asid silfirik (H2SO4), elatriye Kontni Silisyòm apre tranpe nan asid se jeneralman pi wo a 99.7%. Pandan pwosesis marinated la, byenke fè, aliminyòm ak lòt eleman yo tou fonn nan asid la ak filtre deyò. Sepandan, Silisyòm reyaji tou ak asid pou jenere SiHCl3 (triklorosilan) oswa SiCl4 (tetrachloride silikon). Sepandan, tou de sibstans ki sou yo nan eta gaz, kidonk apre marinated, enpurte orijinal yo tankou fè ak aliminyòm yo te fonn nan asid la, men Silisyòm te vin gaz. Finalman, segondè-pite gaz SiHCl3 oswa SiCl4 redwi ak idwojèn pou jwenn Silisyòm polikristalin ki gen pite segondè.

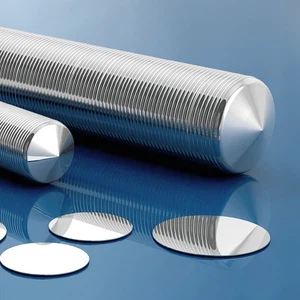

Metòd CZ la pwodui yon sèl kristal Silisyòm:Silisyòm wafers yo pwensipalman itilize nan lojik ak memwa chips, ak yon pati nan mache apeprè 95%; metòd la CZ soti nan desen Czochralski nan filaman mens soti nan metal fonn nan 1918, kidonk li yo rele tou metòd la CZ. Sa a se teknoloji endikap pou grandi Silisyòm kristal sèl jodi a. Pwosesis prensipal la se mete Silisyòm polikristalin nan yon creuset, chofe li pou fonn li, ak Lè sa a, kranpon yon sèl kristal Silisyòm grenn kristal ak sispann li pi wo a creuze a. Lè w ap rale l vètikal, yo mete yon bout nan fonn jiskaske li fonn, epi li tou dousman vire epi rale anwo. Nan fason sa a, koòdone ki genyen ant likid la ak solid la pral piti piti kondanse pou fòme yon kristal sèl. Depi pwosesis la tout antye ka konsidere kòm yon pwosesis pou repwodui kristal grenn nan, kristal Silisyòm pwodwi a se yon sèl Silisyòm kristal. Anplis de sa, se dopaj la nan wafer la tou te pote soti nan pwosesis la nan rale kristal la sèl, anjeneral nan faz likid dopaj ak faz gaz dopaj. Dopaj faz likid refere a adisyon nan eleman P-tip oswa N-kalite nan crucible a. Pandan pwosesis la nan rale kristal sèl, eleman sa yo ka dirèkteman rale nan baton an Silisyòm.

▲ CZ Faraday metòd kristal sèl

▲ Silisyòm baton apre rale yon sèl kristal

Dyamèt woule:Depi li difisil pou kontwole dyamèt baton sèl kristal Silisyòm pandan pwosesis rale yon sèl kristal, yo nan lòd yo jwenn baton Silisyòm estanda dyamèt, tankou 6 pous, 8 pous, 12 pous, elatriye Apre rale a. sèl kristal, dyamèt ingot Silisyòm lan pral woule. Sifas baton an Silisyòm apre woule se lis ak erè gwosè a pi piti.

Koupe chanfreinaj:Apre w fin jwenn ingot Silisyòm lan, wafer la koupe. Se lengote Silisyòm nan mete sou yon machin koupe fiks epi koupe dapre pwogram nan koupe seri. Depi epesè nan wafer Silisyòm lan piti, kwen nan wafer Silisyòm koupe a trè byen file. Objektif chanfreinaj se pou fòme yon kwen lis. Chamfered Silisyòm wafer a gen yon pi ba sant estrès, ki fè li pi solid epi li pa fasil kraze nan manifakti chip nan lavni.

Polisaj:Objektif prensipal polisaj la se fè sifas la nan wafer la douser, plat ak domaj-gratis, epi asire konsistans nan epesè nan chak wafer.

Anbalaj tès:Apre ou fin jwenn wafer Silisyòm poli a, pwopriyete elektrik wafer Silisyòm lan bezwen teste, tankou rezistivite ak lòt paramèt. Pifò faktori wafer Silisyòm gen sèvis wafer epitaxial. Si epitaxial wafers yo bezwen, epitaxial wafer kwasans yo pral pote soti. Si wafer epitaxial la pa nesesè, li pral pake epi anbake nan lòt faktori wafer epitaxial oswa faktori wafer.

Metòd fonn zòn (FZ):Silisyòm wafers ki fèt pa metòd sa a yo pwensipalman itilize nan kèk bato pouvwa, ak yon pati nan mache nan apeprè 4%; Silisyòm wafers fèt pa FZ (zòn k ap fonn metòd) yo pwensipalman itilize kòm aparèy pouvwa. Ak gwosè a nan gaufrèt Silisyòm se sitou 8 pous ak 6 pous. Kounye a, apeprè 15% nan gaufre Silisyòm yo fèt pa metòd k ap fonn zòn. Konpare ak silisyòm wafers ki fèt pa metòd CZ, karakteristik nan pi gwo nan metòd FZ se ke li gen relativman wo rezistivite, pite pi wo, epi li ka kenbe tèt ak vòltaj segondè, men li difisil pou fè gwo-gwosè wafers, ak pwopriyete yo mekanik yo pòv, Se konsa, li se souvan itilize pou aparèy pouvwa Silisyòm wafers, epi li se raman itilize nan sikui entegre.

Gen twa etap nan fè baton Silisyòm kristal sèl pa metòd k ap fonn zòn:

1. Chofe Silisyòm polikristalin, kontakte ak kristal grenn, epi vire anba pou rale yon sèl kristal. Nan yon chanm fou anba vakyòm oswa anviwònman gaz inaktif, sèvi ak jaden elektrik pou chofe baton Silisyòm polikristalin jiskaske Silisyòm polikristalin nan zòn chofe a fonn pou fòme yon zòn fonn.

2. Kontakte zòn nan fonn ak kristal grenn epi fonn li.

3. Lè w deplase pozisyon chofaj jaden elektrik la, zòn nan fonn sou polysilicon la deplase anlè kontinyèlman, pandan y ap kristal grenn nan tou dousman wotasyon ak detire anba, piti piti fòme yon sèl baton Silisyòm kristal. Paske metòd la fonn zòn pa sèvi ak yon kreze, anpil sous polisyon yo evite, ak kristal sèl la rale pa metòd la fonn zòn gen karakteristik pite segondè.

▲ FZ Farad yon sèl estrikti espas kristal

▲ Dyagram chema nan rale sèl kristal FZ

2. Pri fabrikasyon

Semiconductor Silisyòm gauf yo gen pi wo kondisyon pou pite ak pwopriyete elektrik pase nouvo enèji Silisyòm wafers, kidonk plis etap pou pirifye ak rezèv materyèl bwit yo mande nan pwosesis fabrikasyon an, sa ki lakòz yon seri pi divès kalite materyèl bwit manifakti. Se poutèt sa, pwopòsyon nan pri materyèl Silisyòm relativman redwi, men pwopòsyon nan depans fabrikasyon yo pral relativman ogmante.

Pou gaufre Silisyòm semi-conducteurs, pri materyèl bwit se pri prensipal la, kontablite pou apeprè 47% nan pri biznis prensipal la. Dezyèm lan se depans fabrikasyon, kontablite pou apeprè 38.6%. Menm jan ak endistri manifakti semi-conducteurs, endistri wafer Silisyòm se yon endistri entansif kapital ak gwo demann pou envestisman byen fiks, ki pral jenere gwo depans fabrikasyon akòz depresyasyon byen fiks tankou machin ak ekipman. Finalman, depans travay dirèk konte pou apeprè 14.4%.

Pami pri materyèl bwit yo nan fabrikasyon wafer Silisyòm, polysilicon se materyèl prensipal la anvan tout koreksyon, kontablite pou apeprè 3 0.7%. Dezyèm lan se materyèl anbalaj, kontablite pou apeprè 17.0%. Depi gauf Silisyòm semi-conducteurs gen gwo kondisyon pou pwòpte ak vakyòm, espesyalman pou gaufr Silisyòm, ki fasil soksid, kondisyon yo pou anbalaj yo pi wo pase sa yo pou nouvo gaufr Silisyòm enèji. Se poutèt sa, nan estrikti a pri, materyèl anbalaj kont pou yon gwo pwopòsyon. Kreze kwatz kont pou apeprè 8.7% nan pri a matyè premyè. Creze kwatz yo itilize nan fabrikasyon semi-conducteurs Silisyòm wafer se tou yon kreze jetab, men pwopriyete fizik ak tèmik kreze a gen plis egzijans. Likid polisaj, wou fanm k'ap pile, ak pad polisaj kont pou 13.8% nan total epi yo pwensipalman itilize nan pwosesis polisaj la Silisyòm.

▲ Estrikti pri operasyon nan endistri Silisyòm nan 2018

▲ Konpozisyon materyèl bwit nan endistri Silisyòm nan 2018

Depans dlo ak elektrisite konte pou apeprè 15% nan pri fabrikasyon an: Nan pri fabrikasyon an, depans total dlo ak elektrisite konte pou apeprè 15% nan pri fabrikasyon an antye, nan ki depans elektrisite yo konte pou apeprè 11.4% ak depans pou dlo. anviwon 3.4%. An tèm de kantite lajan ki koresponn, dapre done finansye 2018 nan Silisyòm Industry Group la, pri total elektrisite ak depans dlo ekivalan a pri a nan materyèl anbalaj, kontablite pou apeprè mwatye nan materyèl la polysilicon. Pri elektrisite a se yon ti kras pi wo pase sa yo ki an kwatz krize pa apeprè 20%.

▲ Pwopòsyon nan depans fabrikasyon endistri Silisyòm nan 2018

▲ Konpozisyon pri pasyèl nan Silisyòm Industry Group nan 2018 (Inite: 10, 000 Yuan)

3, Kat baryè nan manifakti wafer Silisyòm

Baryè yo nan gauf Silisyòm yo relativman wo, espesyalman pou gauf Silisyòm semi-conducteurs. Gen kat baryè prensipal: baryè teknik, baryè sètifikasyon, baryè ekipman, ak baryè kapital.

▲ Baryè prensipal yo nan endistri manifakti wafer Silisyòm

Baryè teknik:Endikatè yo teknik nan gauf Silisyòm yo relativman gwo. Anplis de gwosè komen an, epesè polisaj, elatriye, gen tou deformation, rezistivite, koub, elatriye nan gaufre Silisyòm. An tèm de endikap 300mm Silisyòm wafers, akòz kondisyon yo inifòmite segondè nan pwosesis avanse pou Silisyòm wafers, konpare ak 200mm wafers, paramèt tankou plat, deformation, koub, ak rezidi metal sifas yo ajoute pou kontwole kondisyon yo ki kalite nan 300mm Silisyòm wafers. . An tèm de pite, pwosesis avanse Silisyòm gaufre yo oblije alantou 9N (99.9999999%) -11 N (99.999999999%), ki se prensipal baryè teknik pou founisè Silisyòm wafer.

Silisyòm wafers yo se pwodwi trè Customized; pite se paramèt ki pi fondamantal nan gaufre Silisyòm ak tou prensipal baryè teknik la. Anplis de sa, wafers Silisyòm yo pa pwodwi inivèsèl epi yo pa ka kopye. Espesifikasyon yo nan gwo gaufret Silisyòm nan divès kalite fondri wafer yo konplètman diferan, ak itilizasyon yo diferan nan divès kalite pwodwi tèminal ap mennen tou nan kondisyon konplètman diferan pou gauf Silisyòm. Sa a mande pou manifaktirè wafer Silisyòm konsepsyon ak fabrike diferan gaufrè Silisyòm selon diferan pwodwi kliyan fen, ki plis ogmante difikilte pou rezèv Silisyòm wafer.

▲ Pwevwa pwofi nan segman biznis konpayi an

Baryè sètifikasyon:Manifaktirè chip yo gen kondisyon strik sou bon jan kalite a nan divès kalite matyè premyè epi yo trè pridan nan chwazi founisè. Gen gwo baryè pou antre nan lis founisè chip manifaktirè yo. Anjeneral, manifaktirè chip yo pral mande pou founisè wafer Silisyòm bay kèk gaufre Silisyòm pou pwodiksyon jijman, ak pi fò nan yo yo te itilize pou wafers tès, pa wafer mas pwodiksyon wafers. Apre yo fin pase wafers tès yo, yo pral pwodwi ti pakèt pwodiksyon an mas. Apre yo fin pase sètifikasyon entèn la, manifakti chip la pral voye pwodwi yo bay kliyan en. Apre yo fin jwenn sètifikasyon kliyan yo, founisè a wafer Silisyòm pral finalman sètifye epi kontra acha a pral siyen. Li pran yon bon bout tan pou pwodwi yo nan semi-conducteurs Silisyòm wafer konpayi yo antre nan chèn ekipman pou manifaktirè chip yo. Sik sètifikasyon pou nouvo founisè pran omwen 12-18 mwa.

Anplis de sa, baryè sètifikasyon yo soti nan gauf tès yo nan gauf pwodiksyon an mas: Kounye a, pi fò nan 12-gaflèt yo pous nan peyi Lachin rete nan rezèv la nan gauf tès yo, men pwosedi yo sètifikasyon pou gaufre tès yo konplètman diferan de sa yo pou wafers pwodiksyon an mas, ak estanda sètifikasyon yo pou pwodiksyon mas Silisyòm wafers yo pi sevè. Depi tès Silisyòm wafers pa fabrike chips, yo sèlman bezwen sètifye pa fonderie wafer tèt li, epi yo sèlman bezwen sètifye nan sit fabrikasyon aktyèl la. Sepandan, pou wafers Silisyòm pwodwi an mas, yo dwe sètifye pa tèminal fabless kliyan ak kontwole nan tout etap nan tout pwosesis fabrikasyon an anvan yo ka apwovizyone yo nan lo. Anjeneral pale, yo nan lòd yo kenbe estabilite nan rezèv Silisyòm wafer ak sede chip. Yon fwa yon manifakti wafer ak yon founisè wafer Silisyòm etabli yon relasyon ekipman pou, yo pa pral fasil chanje founisè, ak tou de pati yo pral etabli yon mekanis fidbak pou satisfè bezwen pèsonalize, ak kolan ant founisè wafer Silisyòm ak kliyan yo ap kontinye ogmante. Si yon nouvo manifakti wafer Silisyòm rantre nan ranje founisè yo, li dwe bay yon relasyon koperativ pi pre ak pi wo kalite Silisyòm wafer pase founisè orijinal la. Se poutèt sa, nan endistri a wafer Silisyòm, kolan ki genyen ant founisè wafer Silisyòm ak manifaktirè wafer se relativman gwo, epi li difisil pou nouvo founisè kraze kolan an.

Baryè ekipman:Ekipman debaz la pou fabrike gaufre Silisyòm se yon sèl gwo founo kristal, ki ka dekri kòm "machin fotolitografi" nan gauf Silisyòm. Founo kristal sèl nan manifaktirè entènasyonal endikap Silisyòm wafer yo tout fabrike poukont yo. Pou egzanp, gwo founo kristal sèl Shin-Etsu ak SUMCO yo fèt poukont yo ak manifaktire pa konpayi an oswa ki fèt ak manifaktire nan kenbe filiales, ak lòt manifaktirè wafer Silisyòm pa ka achte yo. Lòt gwo Silisyòm wafer manifaktirè yo gen pwòp endepandan yon sèl kristal fou founisè yo epi siyen akò konfidansyalite strik, ki fè li enposib pou ekstèn Silisyòm wafer manifaktirè yo achte, oswa yo ka sèlman achte òdinè founo kristal sèl, men yo pa ka bay gwo-spesifikasyon sèl kristal fou. . Se poutèt sa, baryè ekipman yo tou rezon an pou kisa manifaktirè domestik yo pa ka antre nan founisè yo endikap nan silisyòm mondyal.

Baryè kapital:Pwosesis fabrikasyon semi-conducteurs Silisyòm wafers se konplèks, ki mande pou achte ekipman pwodiksyon avanse ak chè, epi tou li mande pou modifikasyon kontinyèl ak debogaj selon diferan bezwen kliyan yo. Akòz gwo depans fiks yo tankou depresyasyon ekipman, chanjman nan demann en gen yon pi gwo enpak sou itilizasyon kapasite konpayi Silisyòm wafer, e konsa sou pwofi konpayi manifakti Silisyòm wafer. An patikilye, konpayi ki fèk antre nan endistri wafer Silisyòm yo te prèske nan yon eta pèt anvan yo te rive nan chajman echèl, epi yo gen gwo kondisyon pou baryè kapital yo. Anplis de sa, akòz sik la sètifikasyon long nan fab wafer pou Silisyòm wafers, manifaktirè wafer Silisyòm bezwen kontinye envesti pandan peryòd sa a, ki tou mande pou anpil lajan.

3. ap toujou wa materyèl semi-conducteurs A pwezan, mache wafer semi-conducteurs domine pa materyèl Silisyòm. Materyèl Silisyòm konte pou apeprè 95% nan tout mache semi-conducteurs. Lòt materyèl yo se sitou konpoze materyèl semi-conducteurs, sitou dezyèm jenerasyon materyèl semi-conducteurs GaAs gauf ak twazyèm-jenerasyon materyèl semi-conducteurs SiC ak GaN. Pami yo, Silisyòm wafers yo se sitou chips lojik, chips memwa, elatriye, epi yo se materyèl ki pi lajman itilize semi-conducteurs. GaAs wafers yo se sitou RF chips, ak senaryo aplikasyon prensipal yo se vòltaj ki ba ak frekans segondè; Materyèl semi-conducteurs twazyèm-jenerasyon yo se sitou gwo-pouvwa ak segondè-frekans chips, ak senaryo aplikasyon prensipal yo se gwo frekans ak gwo pouvwa.

▲ Rapò materyèl wafer

▲ Dimansyon aplikasyon wafers nan diferan materyèl

Semi-conducteurs konpoze ak materyèl Silisyòm yo pa nan yon relasyon konpetitif, men yon relasyon konplemantè; lwa devlòpman materyèl semi-conducteurs (espesyalman wafers, substrats ak epitaxial wafer materyèl) genyen twa wout, sètadi gwosè, vitès ak pouvwa, ak twa wout yo koresponn ak premye, dezyèm ak twazyèm jenerasyon materyèl semi-conducteurs.

▲ Konparezon pèfòmans nan materyèl premye / dezyèm / twazyèm jenerasyon

Materyèl semi-conducteurs premye jenerasyon:Wout gwo-gwosè: Materyèl semi-conducteurs premye jenerasyon yo refere a materyèl Silisyòm. Materyèl Silisyòm yo se materyèl wafer ki pi bonè devlope, epi tou se materyèl ki gen teknoloji ki pi matirite, pri ki pi ba a, ak chèn endistriyèl ki pi konplè nan etap sa a. An menm tan an, kòm gwosè a nan gaufre Silisyòm ogmante, pri a nan yon sèl chip diminye. Zòn aplikasyon prensipal yo se chips lojik ak ba-vòltaj, jaden ki ba-pouvwa. Gwosè gaufrèt Silisyòm yo varye ant 2 pous, 4 pous, 6 pous, 8 pous, ak teknoloji wafer endikap jodi a 12-pous. Tipik konpayi wafer Silisyòm yo enkli Japon an Shin-Etsu Chimik, Sumco, elatriye Kounye a, prensipal fab entènasyonal wafer yo sèvi ak materyèl Silisyòm kòm materyèl pwodiksyon prensipal la.

▲ Konparezon diferan gwosè wafer

Dezyèm jenerasyon materyèl semi-conducteurs:wout gwo vitès. Depi chip la bezwen pou kapab kenbe tèt ak segondè-frekans oblije chanje nan kous la RF, yo te envante wafer nan semiconductor dezyèm jenerasyon. Jaden aplikasyon prensipal la se sikwi RF, ak jaden tèminal tipik la se chip RF nan tèminal mobil tankou telefòn mobil. Semi-conducteurs dezyèm jenerasyon an reprezante sitou pa GaAs (arsenide galyòm) ak InP (fosfid endyòm), pami ki GaAs se materyèl ki souvan itilize tèminal mobil RF chip jodi a. Konpayi fondri tipik yo enkli Taiwan Win Semiconductors, Macronix, Skyworks, Qorvo, elatriye, ki se konpayi RF chip IDM. Endikap aktyèl la se wafers 4-pous ak 6-pous.

Materyèl semi-conducteurs twazyèm jenerasyon:wout gwo pouvwa: prèske nan menm pwen an kòmanse, ak plis opòtinite yo. Wout twazyèm lan se ogmante pouvwa a, ki pral ankouraje aplikasyon toupatou li yo nan jaden an nan sikui gwo pouvwa. Materyèl prensipal yo se SiC ak GaN. Tèminal prensipal yo se endistriyèl, otomobil ak lòt jaden. Wout pouvwa a devlope chips IGBT sou materyèl Silisyòm, pandan y ap materyèl SiC (carbure Silisyòm) ak GaN (nitrure galyòm) gen pi wo pèfòmans pase IGBT. Kounye a, SiC wafers yo se sitou 4-pous ak 6-pous, ak materyèl GaN yo se sitou 6-pous ak 8-pous. Fondasyon pi gwo nan mond lan gen ladan Cree ak Wolfspeed nan Etazini ak X-Fab nan Almay. Sepandan, nan jaden sa a, devlopman gran entènasyonal yo tou relativman dousman. Konpayi domestik yo tankou Sanan Optoelectronics, byenke gen toujou yon sèten diferans nan nivo teknoloji, yo nan etap inisyal la nan endistri a tout antye epi yo gen plis chans kraze monopoli etranje a ak okipe yon plas nan kat jeyografik la fondasyon pouvwa entènasyonal.

Materyèl konpoze mande pou substrate Silisyòm:Malgre ke gen kounye a yon gwo kantite chips SiC ak GaN wafer, tankou chajè yo GaN pibliye pa Xiaomi, OPPO, ak Realme, ak modèl la te pibliye pa Tesla itilize SiC MOSFET olye pou yo IGBT. Sepandan, pou wafers, pifò chips semi-conducteurs konpoze kounye a itilize Silisyòm gauf kòm substrats, ak Lè sa a, fè konpoze epitaxial wafers, ak Lè sa a, fè chips sou wafers epitaxial.

Pri a nan gauf semi-kondiktè konpoze se relativman wo:Koulye a, akòz enkonplè nan chèn nan endistri semi-conducteurs konpoze, kapasite nan pwodiksyon semi-conducteurs konpoze se ba ak pri a nan plak semi-conducteurs konpoze se relativman wo. Sa a mennen nan akseptasyon itilizatè fen ki ba, ak solisyon an endikap pou elektwonik konsomatè se toujou "substra Silisyòm + konpoze epitaxial wafer". Nan jaden otomobil la, IGBT ki baze sou Silisyòm se toujou solisyon endikap la. Silisyòm ki baze sou IGBT chips gen pri ki ba ak yon pakèt vòltaj si ou vle. Pri aparèy SiC MOSFET se 6 a 10 fwa IGBT ki baze sou Silisyòm. Konpare paramèt pèfòmans SiC-MOSFET ak Si-IGBT anba paramèt teknik Infineon 650V/20A, SiC-MOSFET toujou siperyè Si-IGBT an tèm de paramèt pèfòmans, men an tèm de pri, SiC-MOSFET se 7 fwa sa a. Si-IGBT. Anplis, kòm sou-rezistans nan aparèy SiC diminye, pri a nan SiC-MOSFET ogmante eksponansyèlman. Pou egzanp, lè rezistans nan se 45 miliohm, SiC-MOSFET a se sèlman $ 57.6, lè rezistans nan se 11 miliohm, pri a se $ 159.11, ak lè rezistans nan egal a 6 miliohm, pri a te rive jwenn. $310.98.

▲ Infineon SiC-MOSFET vs Si-IGBT Konparezon

▲ Pri Infineon SiC-MOSFET ak relasyon sou rezistans

4, efò domestik yo te kreye gwo potansyèl mache.

1. Silisyòm wafer mache a ap antre nan yon sik kwasans.

Pwopòsyon materyèl fabrikasyon semi-conducteurs ogmante ane pa ane. Materyèl semi-kondiktè yo ka divize an materyèl anbalaj ak materyèl fabrikasyon (ki gen ladan gaufrè Silisyòm ak divès kalite pwodwi chimik, elatriye). Nan yon tan ki long, materyèl semi-conducteurs manifakti ak materyèl anbalaj yo nan menm tandans. Sepandan, depi 2011, ak devlopman kontinyèl nan pwosesis avanse, konsomasyon nan materyèl fabrikasyon semi-conducteurs te piti piti ogmante, ak diferans ki genyen ant materyèl fabrikasyon ak materyèl anbalaj piti piti ogmante. Nan 2018, lavant materyèl fabrikasyon yo te 32.2 milya dola ameriken, ak lavant materyèl anbalaj yo te 19.7 milya dola ameriken, ak materyèl fabrikasyon yo te apeprè 1.6 fwa sa a materyèl anbalaj. Pami materyèl semi-conducteurs, materyèl fabrikasyon konte pou apeprè 62% ak materyèl anbalaj kont pou 38%.

▲ Pwopòsyon konsomasyon materyèl semi-conducteurs nan 2018

▲ Semiconductor fabrikasyon materyèl pri rapò

Silisyòm wafers yo se pi gwo consommables nan manifakti semi-conducteurs; pami materyèl fabrikasyon, Silisyòm wafers, kòm matyè premyè nan semi-conducteurs, kont pou pwopòsyon nan pi gwo, rive 37%. Depi 2017, ak defèt Lee Sedol pa "AlphaGo", nouvo teknoloji zetwal ki te dirije pa entèlijans atifisyèl yo te teknoloji prensipal yo kondwi devlopman nan semi-conducteurs mondyal. An patikilye, nan 2018, demann mondyal la pou memwa te monte, makonnen ak epidemi teknoloji blockchain, ak demann pou wafers Silisyòm te frape yon gwo. Ogmantasyon nan anbakman semi-conducteurs mondyal tou te kondwi ogmantasyon rapid nan chajman wafer Silisyòm. An tèm de anbakman, nan 2018, zòn chajman wafer Silisyòm mondyal la depase 10 milya pous kare pou premye fwa, rive nan 12.7 milya pous kare. Nan 2019, akòz friksyon komès nan premye mwatye ane a, zòn chajman an diminye a 11.8 milya pous kare. An tèm de woulman mache, lavant mache mondyal la nan 2018 te US $ 11.4 milya dola, ak nan 2019 li te rive nan US $ 11.2 milya dola.

▲2009-2019 Zòn Global Silisyòm Shipment Wafer

▲2009-2019 Komèsyal mondyal Silisyòm Wafer

Soti nan pèspektiv nan segmentasyon wafer, akòz pri a wo nan dezyèm jenerasyon ak twazyèm jenerasyon materyèl semi-conducteurs, ak lefèt ke pifò semi-conducteurs konpoze yo baze sou Silisyòm wafers, Silisyòm wafers kont pou 95% nan substra wafer mondyal. Soti nan pèspektiv nan gwosè espesifik wafer, 12-pous wafers yo se kalite prensipal la nan gauf mondyal Silisyòm. An 2018, 12-pous wafers te reprezante 64% nan anbakman mondyal Silisyòm wafers, ak 8-pous wafers te konte pou 26%.

▲Silisyòm wafer chajman rapò pa gwosè

Soti nan pèspektiv aplikasyon tèminal yo, konsomasyon mondyal la nan 12-pous wafers se sitou memwa chips, ak Nand Flash ak memwa DRAM kontablite pou apeprè 75% nan total, nan ki Nand Flash konsome apeprè 33% nan wafers, ak Nand flash gen 35% nan mache a en nan mache a smartphone. Li ka wè ke ogmantasyon nan chajman smartphone ak kapasite se faktè prensipal ki kondwi chajman nan 12-pous wafers. Pami 12-pous wafers, chips lojik konte pou apeprè 25%, DRAM kont pou apeprè 22.2%, ak lòt chips tankou CIS kont pou apeprè 20%.

2. Lachin nan semi-conducteurs Silisyòm wafer mache gen espas gwo

Mache materyèl semi-conducteur Lachin nan te grandi piti piti. Nan 2018, lavant mondyal materyèl semi-conducteurs te rive nan 51.94 milya dola ameriken, yon ogmantasyon ane sou ane de 10.7%. Pami yo, lavant Lachin nan te US $ 8.44 milya dola. Kontrèman ak mache mondyal la, lavant materyèl semi-conducteur Lachin nan yo te ap grandi depi 2010, epi yo te grandi nan yon pousantaj de plis pase 10% pou twa ane youn apre lòt soti nan 2016 a 2018. Mache mondyal la semi-conducteurs materyèl anpil afekte pa faktè siklik, espesyalman nan Taiwan. , Lachin ak Kore di Sid, kote fluctuations yo gwo. Mache Nò Ameriken ak Ewopeyen yo prèske nan yon eta de kwasans zewo. Materyèl semi-conducteurs Japon yo te nan yon eta de kwasans negatif pou yon tan long. Globalman, se sèlman mache materyèl semi-conducteurs nan tè pwensipal Lachin nan yon fenèt kwasans alontèm. Mache materyèl semi-conducteur Chinwa a se nan gwo kontra ak mache mondyal la.

▲ Lavant mondyal materyèl semi-conducteurs ak to kwasans (an milya dola ameriken)

▲ Lavant anyèl materyèl semi-conducteurs pa peyi ak rejyon (Inite: milya dola ameriken)

Materyèl semi-conducteurs mondyal yo piti piti deplase nan mache tè pwensipal Chinwa a. Soti nan lavant pataje nan divès peyi ak rejyon yo, twa pi gwo peyi yo oswa rejyon yo te konte pou 55% nan 2018, ak efè konsantrasyon rejyonal la evidan. Pami yo, Taiwan, Lachin konte pou apeprè 23% nan kapasite pwodiksyon wafer mondyal la, ki fè li rejyon an ak pi gwo kapasite pwodiksyon nan mond lan. Lavant materyèl semi-conducteurs li yo se US $ 11.4 milya dola, kontablite pou 22% nan mond lan, plase an premye, e li te pi gwo rejyon konsomasyon materyèl semi-conducteurs nan mond lan pou nèf ane konsekitif. Kore di sid konte pou apeprè 20% nan kapasite pwodiksyon wafer mondyal la, ak lavant materyèl semi-conducteurs nan US $ 8.72 milya dola, kontablite pou 17%, plase dezyèm fwa. Kontinent Lachin kont pou apeprè 13% nan kapasite pwodiksyon mondyal la, ak lavant materyèl semi-conducteurs nan US $ 8.44 milya dola, kontablite pou apeprè 16% nan mond lan, plase twazyèm. Sepandan, nan yon peryòd tan ki long, pati nan mache materyèl semi-conducteurs nan tè pwensipal Lachin te ogmante ane pa ane, soti nan 7.5% nan 2007 a 16.2% nan 2018. Materyèl semi-conducteurs mondyal yo piti piti deplase nan mache tè pwensipal Chinwa a.

▲ Pataje lavant pa peyi ak rejyon an 2018

▲ Lavant materyèl semi-conducteurs ak pataje nan tè pwensipal Lachin (an milya dola ameriken)

Kapasite mondyal pwodiksyon wafer pral inogire nan kwasans eksplozif. Fab wafer 12-pous la, ki reprezante teknoloji ki pi avanse nan fab wafer jodi a, te nan pi gwo konstriksyon nan ane 2017 a 2019, ak yon mwayèn de 8 12-fab wafer pous te ajoute chak ane atravè lemond. Yo estime ke nan 2023, pral gen 138 12-pous wafer fab nan mond lan. Dapre estatistik IC Insight, akòz ensètitid nan lagè komès Sino-US nan premye mwatye nan 2019, gwo fab wafer atravè mond lan ranvwaye plan ogmantasyon kapasite yo, men yo pa t 'anile yo. Avèk rekiperasyon komès Sino-US nan dezyèm mwatye nan 2019 ak epidemi mache 5G la, kapasite pwodiksyon wafer mondyal la nan 2019 toujou kenbe yon ogmantasyon de 7.2 milyon moso. Sepandan, ak rive nan vag ranplasman mache 5G la, kapasite pwodiksyon wafer mondyal la pral inogire nan yon peryòd pik nan ogmantasyon soti nan 2020 a 2022, ak ogmantasyon nan twa ane nan 17.9 milyon dola moso, 20.8 milyon dola moso ak 14.4 milyon moso respektivman, ak pral mete yon gwo rekò nan 2021. Kapasite wafer sa yo pral nan Kore di sid (Samsung, Hynix), Taiwan (TSMC) ak tè pwensipal Lachin (Yangtze River Depo, Changxin Depo, SMIC, Huahong Semiconductor, elatriye). Mainland Lachin pral kont pou 50% nan ogmantasyon kapasite a.

▲ Kantite 12-pous wafer fab atravè lemond, 2002-2023

▲ Ogmante kapasite pwodiksyon mondyal (inite: milyon moso/ane, 8-pous wafer ekivalan)

Konstriksyon wafer fabs nan tè pwensipal Lachin pral inogire nan yon peryòd de kwasans rapid. Depi 2016, tè pwensipal Lachin te kòmanse aktivman envesti nan konstriksyon wafer fabs, ak yon vag nan konstriksyon faktori yo te mete nan. Dapre pwevwa SEMI a, 62 fab wafer yo pral bati ak mete nan pwodiksyon nan mond lan soti nan 2017 a 2020, nan ki 26 yo pral nan Lachin, kontablite pou 42% nan total la. Kantite konstriksyon an 2018 te 13, sa ki reprezante 50% ekspansyon an. Rezilta ekspansyon an oblije mennen nan yon ogmantasyon nan depans kapital ak depans ekipman pou fab wafer. Dapre SEMI, pa 2020, kapasite enstale wafer fabs nan tè pwensipal Lachin pral rive nan 4 milyon 8-pous wafers ekivalan pa mwa, konpare ak 2.3 milyon dola nan 2015, ak yon to kwasans konpoze anyèl 12%, ki se pi wo pase lòt rejyon yo. An menm tan an, gwo fon nasyonal la tou envesti lou nan endistri manifakti semi-conducteurs. Nan premye faz nan envestisman Big Fon an, endistri manifakti a te konte pou 67%, byen lwen pi wo pase endistri konsepsyon ak endistri anbalaj ak tès.

▲2010-2020 Envestisman fab semi-conducteur Lachin nan (Inite: 100 milyon dola ameriken)

▲ Rapò envestisman nan premye faz nan Gwo Fon Nasyonal la

Apati fen ane 2019 la, gen toujou 9 8-fab wafer pous ak 10 12-fab wafer pous sou konstriksyon oswa planifikasyon nan peyi Lachin. Anplis de sa, depi pi fò nan fab wafer 12-pous Lachin nan yo kounye a nan pwodiksyon jijman oswa pwodiksyon ti-pakèt, yo nan pati anba a nan kapasite pwodiksyon an. Apre ou fin jwenn verifikasyon pwodwi nan men kliyan yo ak verifikasyon sou mache a, kapasite pwodiksyon an pral antre nan yon faz ranp-up, epi pral gen yon gwo demann pou matyè premyè en.

▲ Nouvo fab wafer nan Lachin

Popilarite a nan 5G te mennen nan yon ogmantasyon nan kontni an Silisyòm nan tèminal: soti nan epòk la nan smartphones kòmanse ak iPhone 3 a, nan telefòn mobil yo 4G reprezante pa iPhone a 5, epi finalman nan epòk aktyèl la nan telefòn mobil 5G. Kontni Silisyòm nan telefòn mobil yo ap kontinye ogmante. Dapre analiz pri materyèl telefòn mobil yo pa demantèlman òganizasyon yo tankou tech insights ak iFixit, valè inite prensipal chips telefòn mobil yo, tankou processeurs telefòn mobil (AP), chips pwosesis baseband (BP), memwa (Nand flash). , DRAM), modil kamera (CIS), chips frekans radyo (RF), chips jesyon pouvwa (PMIC), chip Bluetooth/wifi, elatriye, te montre yon ogmantasyon gradyèl, ak pwopòsyon valè total inite a ogmante. ane pa ane. Malgre ke nan etap nan iPhone X, pwopòsyon nan chips diminye akòz chanjman nan ekran an, ak optimize ki vin apre kontinyèl, pwopòsyon nan pri chip te ogmante tou ane pa ane. Nan epòk iPhone 11 pro max, pik telefòn mobil 4G yo, pwopòsyon chips prensipal yo te rive nan 55%, ak valè yon sèl inite se apeprè 272 dola ameriken. Nan evolisyon soti nan iPhone 3 a iPhone 11 Pro Max, kamera telefòn mobil lan te chanje soti nan yon sèl piki a 3 vaksen, memwa kò a te ogmante de 8GB a 512GB, pwopòsyon de kontni Silisyòm pou chak inite te ogmante de 37% a 55%. , ak valè pou chak inite ogmante soti nan US $ 68 a US $ 272.

2020 se premye ane pwodiksyon an mas telefòn mobil 5G. Dapre analiz demonte Samsung S20 ak Xiaomi 10 telefòn mobil yo ki te lage, valè ak pwopòsyon chips prensipal yo pou chak inite yo te ogmante plis konpare ak telefòn mobil 4G. Pou Samsung, chips prensipal yo konte pou 63.4% nan pri total materyèl, ak valè pou chak inite te rive nan US $ 335, ki se 23% pi wo pase iPhone 11 Pro Max. Pou Xiaomi, pwopòsyon nan chips prensipal yo se menm pi wo, rive nan 68.3%, ak valè a pou chak inite nan chips prensipal yo te tou rive nan US $ 300. Dapre demonte Samsung S20 ak Xiaomi 10, li estime ke chips prensipal yo nan premye telefòn mobil 5G yo pral konte pou apeprè 65% ~ 70%, ak valè yon sèl machin pral alantou US $ {{18} }.

▲BOM dekonpozisyon pri smartphones endikap yo

▲ Pri rapò nan chip prensipal yo nan diferan telefòn mobil

Konstriksyon wafer fabs ogmante demann pou Silisyòm gaufrèt: ekspansyon kapasite wafer fab pral inevitableman mennen nan yon ogmantasyon nan demann lan pou gaufrè Silisyòm. Koulye a, Lachin te envesti lou nan fabs wafer, fòme yon endistri memwa domine pa Yangtze memwa teknoloji ak Hefei Changxin, yon endistri chip lojik domine pa SMIC, yon liy pwodiksyon pwosesis espesyal domine pa Huahong Semiconductor ak Jetta Semiconductor, ak yon fondri aparèy pouvwa. domine pa Lachin Resous Microelectronics ak Silan Microelectronics. Koulye a, to kwasans lan nan lavant wafer Silisyòm nan tè pwensipal Lachin nan 2017/2018 se pi wo pase 40%. Ak benefisye de tandans nan gwo envestisman fon ak sibstitisyon domestik, en wafer fabs te konplètman elaji kapasite pwodiksyon yo, kondwi yon ogmantasyon nan demann pou en silisyòm wafers. Dapre pwevwa SUMCO a, nan 2020, demann pou 8-pous Silisyòm wafers nan tè pwensipal Lachin pral apeprè 970,000 moso, ak 12-pous wafers pral rive nan 1.05 milyon moso.

▲ Lachin tè pwensipal Silisyòm wafer lavant ak to kwasans (Inite: milya dola ameriken)

▲ Chanjman nan demann wafer Silisyòm nan tè pwensipal Lachin (inite: 10, 000 moso / mwa)

Sik ogmantasyon pri + pwosesis avanse ankouraje ogmantasyon "pri": Dapre kalkil istorik pri wafer Silisyòm lan, li se kounye a nan kòmansman yon nouvo wonn sik ogmantasyon pri. Soti nan 2009 rive 2011, smartphones byen vit te vin popilè, kontni Silisyòm nan telefòn mobil yo te ogmante, ak pri Silisyòm pou chak inite zòn te kontinye ap monte, rive $1.09/pous kare an 2011. Pita , ak ogmantasyon nan envantè wafer Silisyòm ak n bès nan lavant smartphone, pri a nan Silisyòm wafers pou chak zòn inite kontinye tonbe, e li te rive nan pwen ki pi ba li yo nan 2016, nan $ 0.67 / pous kare. Nan 2016, "AlphaGo" Google la te bat Lee Sedol, sa ki pèmèt entèlijans atifisyèl antre nan etap nan istwa. Demann mondyal la pou wafers Silisyòm ogmante, antre nan yon nouvo wonn nan sik ogmantasyon pri. Avèk liberasyon telefòn mobil 5G yo nan 2019, pri silisyòm wafers pou chak inite zòn te rive nan $0.94. Avèk lage gwo echèl telefòn mobil 5G yo an 2020, sa ki lakòz demann mondyal pou wafers Silisyòm, li espere ke pral gen 2-3 ane nan espas ogmantasyon pri alavni.

Pwosesis avanse ogmante pri; gauf Silisyòm semi-conducteurs yo se materyèl debaz pou fabrikasyon chip, ak nenpòt fluctuations nan bon jan kalite pral gen yon enpak grav sou chips yo. Avèk devlopman kontinyèl nan pwosesis avanse, kondisyon yo ki enpurte pou gaufre Silisyòm semi-conducteurs yo ap vin pi wo ak pi wo. Kondisyon ki pi wo fè pwosesis fabrikasyon silisyòm wafers pi difisil, kidonk pri a ap vin pi wo ak pi wo. Pou egzanp, pou menm 12-pous Silisyòm wafers, pri 7nm pwosesis Silisyòm wafers se 4.5 fwa pri 90nm Silisyòm wafers. Kounye a, fab wafer yo nan tè pwensipal Lachin yo sitou bati ak 12-pous wafers, ak pri a nan wafers Silisyòm se pi wo pase sa yo ki nan 8-pous wafers. An menm tan an, fondri chip lojik ki reprezante pa SMIC ak Huahong Semiconductor te piti piti transfere pwosesis la soti nan 28nm a 16/14nm pwosesis, ki te ogmante pri a an jeneral nan gauf Silisyòm.

Depi liy fabrikasyon 12-pous la te premye louvri nan mond lan an 2000, demann sou mache a te ogmante anpil. An 2008, volim chajman an te depase 8-pous Silisyòm wafers la pou premye fwa, ak nan 2009 li depase sòm total la nan zòn chajman nan lòt gwosè nan Silisyòm wafers. Soti nan 2016 a 2018, akòz devlopman en nan mache émergentes tankou AI, cloud computing, ak blockchain, pousantaj kwasans konpoze anyèl 12-pous Silisyòm wafers te 8%. Nan tan kap vini an, pati nan mache nan 12-pous Silisyòm wafers yo ap kontinye ogmante. Dapre done SUMCO yo, pral toujou gen yon diferans nan rezèv mondyal la ak demann nan 12-pous Silisyòm wafers nan pwochen 3-5 ane yo, ak diferans la ap vin pi gwo ak pi gwo kòm pwosperite nan semi-conducteurs la. sik ogmante. Pa 2022, pral gen yon espas 1000K / mwa. Kòm yon baz manifakti semi-conducteurs émergentes nan mond lan, gwo gap Silisyòm wafer Lachin nan pral ankouraje vitès la nan lokalizasyon wafer Silisyòm.

Selon estatistik SUMCO, kantite lavant Silisyòm gaufrèt nan tè pwensipal Lachin nan 2018 te apeprè 930 milyon dola ameriken, yon ogmantasyon de 45% ane sou ane, sa ki fè li mache wafer Silisyòm k ap grandi pi rapid nan mond lan. Benefisye de plan ekspansyon gwo fab wafer tankou Yangtze memwa, SMIC, ak Changxin Depo nan 2020-2022. Yo estime ke nan fen 2022, demann lan pou silisyòm wafers ekivalan 12-pous nan tè pwensipal Lachin pral rive nan 2.01 milyon dola pa mwa, ak yon espas mache nan 20 milya dola Yuan.

Sibranch kwè ke kòm benefisyè a nan twazyèm transfè a nan endistri a semi-conducteurs, pati nan lavant semi-conducteurs peyi mwen an nan mache mondyal la ap kontinye ap monte. Anplis de sa, peyi mwen an se pi gwo pwodiktè, ekspòtatè ak konsomatè nan mond lan nan pwodwi elektwonik konsomatè, e li gen yon gwo demann pou pwodwi semi-conducteurs. Se poutèt sa, nivo lokalizasyon pral gen yon gwo enpak sou sekirite endistriyèl. Kòm varyete nan pi gwo ak pi fondamantal nan mache a materyèl fabrikasyon wafer, peyi mwen an gen enpèfeksyon nan jaden an nan Silisyòm gauf, e sa a se pi enpòtan nan gwo Silisyòm gauf. Sepandan, ak sipò politik nasyonal yo ak lajan, anpil konpayi Chinwa yo te planifye pwodiksyon liy yo ak mete deyò gwo gaufret Silisyòm semiconductor.